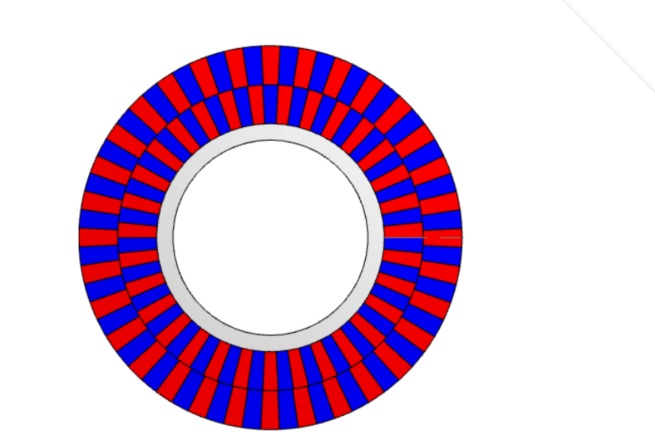

双码道磁盘/磁环通过内外两圈磁极的相位差实现更高分辨率,其设计与磁编码器芯片如IC-Haus配合需满足以下关键技术要求:

1. 磁极的精密排布

相位差设计:

主码道(Track 1)与副码道(Track 2)的磁极间距需满足 游标原理(如主轨周期为λ,副轨周期为λ±Δλ),通过相位差Δθ实现细分。

例如:主轨周期λ=2mm,副轨周期λ’=1.95mm,每圈可细分至0.05mm分辨率。

现有产品包括32/31对极,64/63对极等设计。

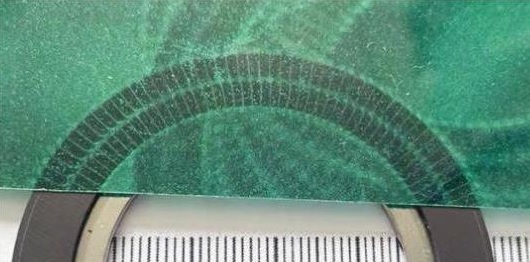

对齐精度:双轨间相对位置误差需小于±5μm,否则会导致细分误差。

2. 磁信号质量与一致性

磁场强度: 表磁强度需满足至少20mT。

磁场强度均匀性:双轨磁化强度差异需小于5%,避免信号幅值波动影响芯片解码。

单对极偏差:需要严格控制在1.5%以内

3.机械结构要求

| 参数 | 要求 |

|---|---|

| 径向跳动公差 | ≤ 0.05 mm(避免气隙变化导致信号波动) |

| 轴向端面平行度 | ≤ 0.03 mm |

| 安装同轴度 | ≤ 0.1 mm(相对轴心) |

| 热膨胀匹配性 | 磁环CTE需与安装轴材料(通常为不锈钢/铝)接近 |

4. 与IC-Haus芯片的协同设计

信号接口匹配:编码盘输出信号需与芯片输入特性兼容(如电压范围0.3V~5V,频率<2MHz)。

- 校准支持:芯片需支持双轨信号的动态校准(如iC-MH系列的自动偏置校正功能)。

- 冗余处理:若采用双轨冗余设计,芯片需支持信号择优或融合算法(如iC-PX系列)。

三、IC-Haus芯片对双轨编码盘的优化支持

IC-Haus系列芯片通过以下技术手段适配双轨游标编码盘的高精度需求:

1. 多通道同步采样

- 支持双轨信号同步采集(如iC-MH8的8通道输入),消除时延导致的相位误差。

2. 高精度插值算法

利用片上DSP对双轨相位差进行实时计算,实现分辨率提升(如从1μm细分至0.1μm)。

3. 动态补偿功能

自动校正安装偏心、磁场不均匀性等误差,降低对编码盘加工精度的依赖。

4. 故障检测与容错

检测双轨信号一致性,在单轨失效时切换至备用轨道(如iC-PX系列)。

四、典型应用场景与选型建议

机器人关节

芯片:iC-MU128(绝对位置)+ 双轨磁性码盘。

优势:结构精简,适应频繁正反转

汽车转向系统

芯片:iC-PX7800(冗余双轨)+ 耐高温编码盘。

优势:ASIL-D功能安全认证,抗振动干扰。

五、设计注意事项

- 编码盘安装:使用非磁性夹具,避免引入外部磁场干扰。

信号走线:双轨信号线需等长、屏蔽,减少传输延迟差异。

校准流程:上电后执行全行程校准,补偿机械装配误差。

通过结合IC-Haus芯片的高性能与双码道磁盘的精密设计,可实现微米级甚至纳米级的位置检测,适用于半导体设备、机器人关节等高精度,有限空间内的位置检测。

以下是我们匹配IC-Haus芯片的标准双码道磁盘产品:

| MU200 | |||||||

| Number of pole pairs on master track | Number of pole pairs on Nonius track | ID2 | 0D2 | Diameter of master track | Diameter of Nonius track | Pole width of master track | Pole width of Nonius track |

| 32 | 31 | 25mm | 44.5mm | 40.8mm | 32.8mm | 2mm | 1.66mm |

| 64 | 63 | 62mm | 85mm | 81.5mm | 73.5mm | 2mm | 1.83mm |

| MU150 | |||||||

| Number of pole pairs on master track | Number of pole pairs on Nonius track | ID2 | 0D2 | Diameter of master track | Diameter of Nonius track | Pole width of master track | Pole width of Nonius track |

| 64 | 63 | 47 | 65 | 61 | 54 | 1.5 | 1.34 |

| 32 | 31 | 18 | 34.5 | 30.6 | 23.4 | 1.5 | 1.34 |

| MU128 | |||||||

| Number of pole pairs on master track | Number of pole pairs on Nonius track | ID2 | 0D2 | Diameter of master track | Diameter of Nonius track | Pole width of master track | Pole width of Nonius track |

| 64 | 63 | 38 | 56 | 52.2 | 45 | 1.28 | 1.12 |

| 32 | 31 | 15 | 29 | 26 | 18.88 | 1.28 | 1.12 |